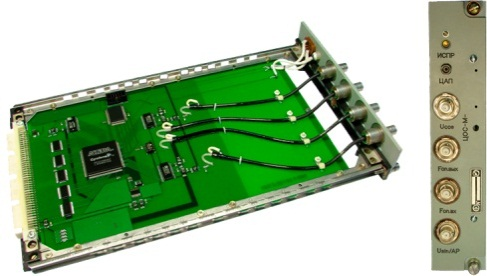

Разработка систем цифровой обработки сигналов на FPGA⁚ Полное руководство

Мир современной электроники немыслим без высокопроизводительных систем цифровой обработки сигналов (ЦОС). От обработки изображений в смартфонах до управления сложными радиолокационными системами – везде используются ЦОС. И одним из наиболее эффективных способов реализации таких систем являются программируемые логические интегральные схемы (FPGA). В этой статье мы подробно рассмотрим ключевые аспекты разработки систем ЦОС на FPGA, начиная с выбора архитектуры и заканчивая отладкой и тестированием. Подготовьтесь к глубокому погружению в мир высокоскоростной обработки данных!

Выбор архитектуры FPGA для ЦОС

Выбор подходящей FPGA – критически важный этап. Необходимо учесть множество факторов, включая требуемую вычислительную мощность, количество входов/выходов, тип используемых интерфейсов (например, PCIe, Ethernet, SPI) и, конечно же, бюджет. Современные FPGA от таких производителей, как Xilinx и Intel (Altera), предлагают широкий спектр решений, от компактных и энергоэффективных до гигантских устройств с невероятной вычислительной мощностью. Важно тщательно проанализировать требования проекта и выбрать FPGA, оптимально соответствующую этим требованиям. Не стоит экономить на вычислительных ресурсах, если это может привести к снижению производительности или невозможности реализации проекта в целом.

Например, для простых задач обработки аудиосигналов может подойти недорогая FPGA с относительно небольшим количеством логических элементов. Однако, для обработки видео в реальном времени или выполнения сложных алгоритмов машинного обучения потребуется значительно более мощная платформа с большим количеством блоков памяти и высокоскоростными интерфейсами.

Критерии выбора FPGA⁚

- Вычислительная мощность (количество логических элементов, блоков памяти)

- Скорость работы (частота тактовой частоты)

- Доступные интерфейсы

- Стоимость

- Поддержка инструментов разработки

Разработка алгоритмов цифровой обработки сигналов

После выбора FPGA необходимо разработать алгоритмы ЦОС. Это может включать в себя проектирование цифровых фильтров, преобразование Фурье, корреляцию сигналов и многие другие операции. Важно оптимизировать алгоритмы для достижения максимальной производительности на выбранной FPGA. Это может потребовать использования специализированных техник, таких как параллельная обработка данных, pipelining и использование аппаратных ускорителей.

На этом этапе также следует учитывать ограничения, накладываемые архитектурой FPGA, такие как ограниченное количество ресурсов и время выполнения операций. Использование инструментов моделирования и симуляции позволяет проверить корректность работы алгоритмов еще до реализации на FPGA.

Реализация на языке VHDL или Verilog

Алгоритмы ЦОС реализуются на языке описания аппаратуры (HDL), таком как VHDL или Verilog. Эти языки позволяют описать аппаратную логику на высоком уровне абстракции. Затем, с помощью инструментов синтеза и размещения, HDL-код преобразуется в конфигурационный файл для FPGA.

Выбор между VHDL и Verilog часто зависит от личных предпочтений разработчика и опыта работы с этими языками. Оба языка имеют свои преимущества и недостатки, и выбор между ними обычно не сильно влияет на конечный результат.

Синтез, размещение и трассировка

После написания HDL-кода, необходимо провести синтез, размещение и трассировку. Синтез преобразует HDL-код в сеть логических элементов. Размещение определяет, какие логические элементы будут использованы для реализации каждой части проекта. Трассировка определяет, как эти элементы будут соединены между собой.

Этот этап является критическим для достижения желаемой производительности системы. Неэффективное размещение и трассировка могут привести к снижению скорости работы и увеличению задержек.

Отладка и тестирование

После синтеза, размещения и трассировки необходимо провести тщательную отладку и тестирование системы. Это включает в себя проверку функциональности системы, измерение производительности и анализ потребляемой мощности;

Для отладки могут использоваться различные методы, включая симуляцию, встроенные средства отладки FPGA и логические анализаторы. Тестирование должно охватывать все возможные сценарии работы системы, чтобы убедиться в ее надежности и стабильности.

Примеры применения

Системы ЦОС на FPGA находят широкое применение в различных областях. Вот несколько примеров⁚

| Область применения | Пример |

|---|---|

| Обработка изображений | Компрессия изображений, распознавание объектов |

| Обработка сигналов связи | Модуляция/демодуляция, кодирование/декодирование |

| Радиолокация | Обработка сигналов радара, обнаружение целей |

| Медицинская техника | Обработка сигналов ЭКГ, МРТ |

| Промышленная автоматизация | Управление процессами, контроль параметров |

Разработка систем ЦОС на FPGA – это сложный, но увлекательный процесс, требующий глубоких знаний в области цифровой обработки сигналов, языков HDL и архитектуры FPGA. Однако, результатом является создание высокопроизводительных, эффективных и гибких систем, способных решать самые сложные задачи в различных областях.

Надеемся, эта статья помогла вам получить общее представление о разработке систем ЦОС на FPGA. В следующих статьях мы рассмотрим более подробно отдельные аспекты этого процесса.

Хотите узнать больше о разработке систем цифровой обработки сигналов на FPGA? Подпишитесь на нашу рассылку и следите за обновлениями на нашем сайте! Мы регулярно публикуем новые статьи и руководства, которые помогут вам в ваших проектах.

Облако тегов

| FPGA | VHDL | Verilog | ЦОС | Цифровая обработка сигналов |

| Xilinx | Altera | Синтез | Размещение | Отладка |